GCC编译

安装GCC编译器

1

sudo apt intsall build-essential

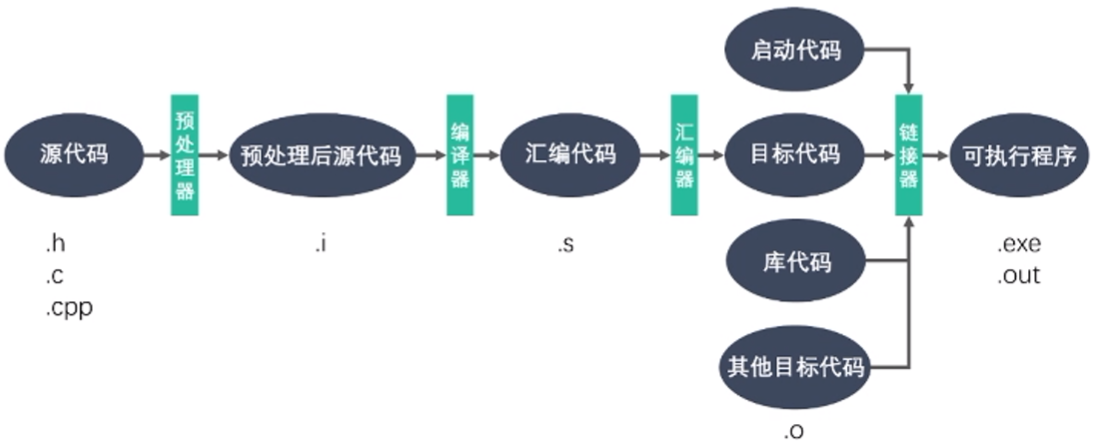

GCC工作流程

预处理阶段会去掉注释,再把头文件内容拷贝到cpp文件中,再替换宏。可用下面这个语句。查看对cpp文件预处理过后的文件

预处理阶段会去掉注释,再把头文件内容拷贝到cpp文件中,再替换宏。可用下面这个语句。查看对cpp文件预处理过后的文件-E选项意味着 预处理指定文件而不进行编译。1

gcc -E test.c -o test.i

``` 代表着 编译指定源文件但是不进行汇编。 1

2

3

```shell

gcc -S test.c -o test.S表示编译、汇编指定的源文件,但是不进行链接,也就是生成目标文件。 1

2

3

```shell

gcc -c test.S -o test.o什么都不加的化会直接生成可执行文件

1

gcc test.c -o a.out

| -g | 该程序可以被调试器调试 |

| —— | :————————————- |

| -D | 在程序编译的时候指定一个宏 |

| -w | 不产生任何警告信息 |

| -l | 编译时使用指定的库 |

| -L | 编译时搜索库的路径 |等等。

Makefile

简介

一个工程中的源文件不计其数(一个项目有有很多的文件),现在的项目基本都是按模块进行划分的,而这些模块存放在若干目录中。makefile中定义了一系列的规则(这些规则定义了一系列如何编译程序的操作,比如哪些文件需要编译、哪些临时文件需要及时的清除等),如此以来我们只需要通过make命令就可以一键编译源程序了。所以常常说makefile带来的最大的好处就是”自动化编译”,因为只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发效率。

make是一个命令工具,它能够解释Makefile文件中的指令,一般来说大多数IDE都具备这样的功能。

原文链接:https://blog.csdn.net/weixin_46120107/article/details/126149556

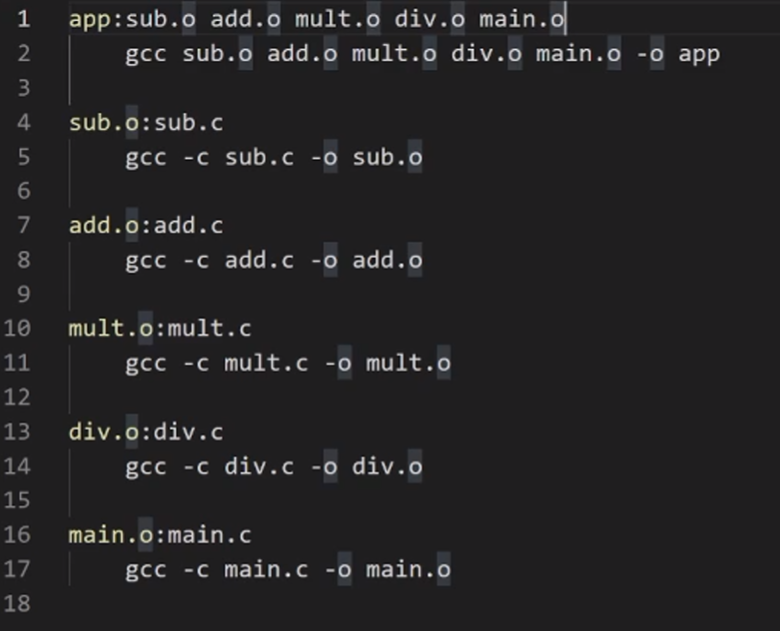

makefile的编写的规则

1 | 目标。。。:依赖。。。 |

目标:最终要生成的文件(伪目标除外)

依赖:生成目标所需要的文件或目标(这里的目标是子目标)

命令:通过执行命令来操作依赖来生成目标

个人认为就是一系列编译指令组成的一个脚本。

上面这个例子,app所需的依赖由其他规则生成,所以要先检查其他规则并执行其他规则。并且他会比较依赖文件的时间,以此检查改动,从而再次make的时候就只执行改变的部分。

上面这个例子,app所需的依赖由其他规则生成,所以要先检查其他规则并执行其他规则。并且他会比较依赖文件的时间,以此检查改动,从而再次make的时候就只执行改变的部分。

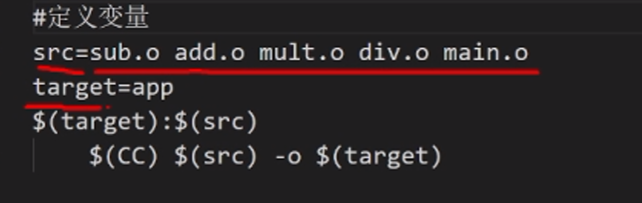

不想一点一点写了,下面一看就懂!!!

变量的定义方式如下:

CC变量是自带的。

(待更新。。。)